隨著AI技術快速發展、高清視頻及自動駕駛等應用不斷普及,對于高性能計算的需求也在提速。相關標準組織同樣加快了新標準的推出,其中高性能計算機的供電電源在供電能力、輸出接口等參數上也在不斷提升。Intel在2022年推出了ATX3.0標準,在電源的峰值功耗方面要求提升巨大。電源整體輸出能力需具備100ms承擔120%額定功率輸出、10ms承擔160%額定功率輸出、1ms承擔180%額定功率輸出、100μs承擔200%額定功率輸出。

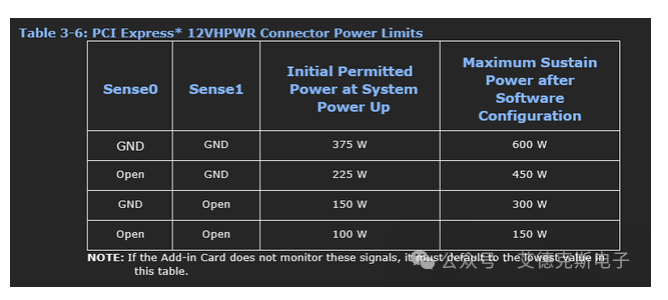

同時PCIe5.0采用16Pin接口,其中4Pin用于通訊,12Pin用于供電,每Pin大承載電流在9.2A,大可以輸出600W供電接口。

圖一PCIe 12V接口功率限值

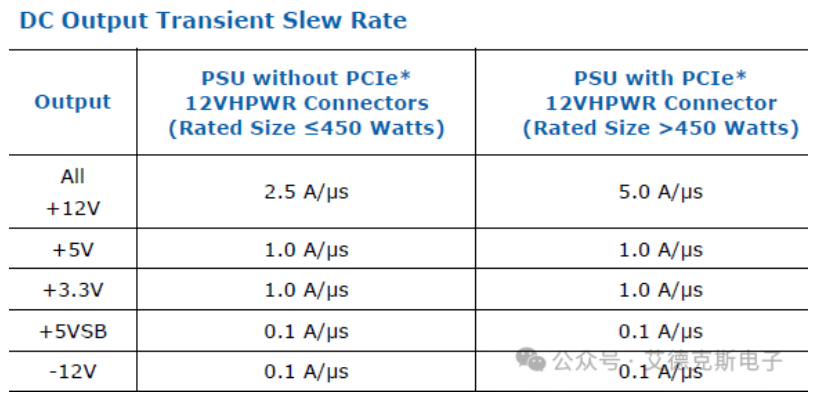

直流電子負載可用來測試電源的輸出特性,除了按照額定電壓及大功率需求選擇電子負載規格外,還需要考慮速度的指標以保證達到電源動態響應測試的要求。在這一測試中直流電子負載的電流上升速度至少要達到5A/μs。

圖二PCIe 12V接口電流上升速率

隨著電子技術的日益發展,對電子負載的要求也變得越來越高,除了高性能計算機電源外還有很多高電流變化率的應用場景。如何提供成熟穩定的產品幫助用戶實現尖端的測試需求,考驗著電子負載制造商的“硬實力”。

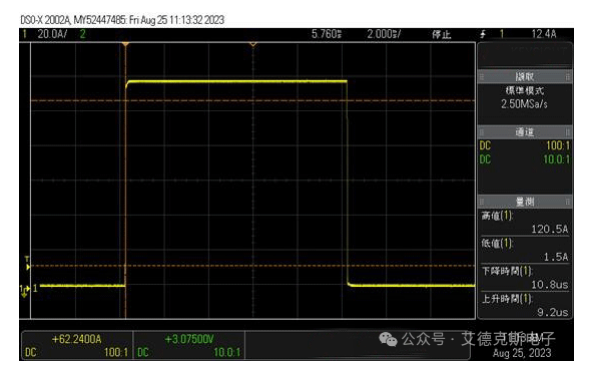

艾德克斯新品IT8700P+系列高速多通道直流電子負載采用機框加模組形式,單機多16通道支持多通道測試,亦可通多主從并機擴展功率。具備高速動態響應,單模組大上升速度12A/μs,可實現電流小上升時間<10μs。單機可實現48A/μs大上升速度。同時更低的導通內阻適合低壓帶載測試。更快的環路速度,可精準控制電流無過沖,提高測試效率。適合于高速電源、超級電容、燃料電池、鋰電池、太陽能電池的測試。

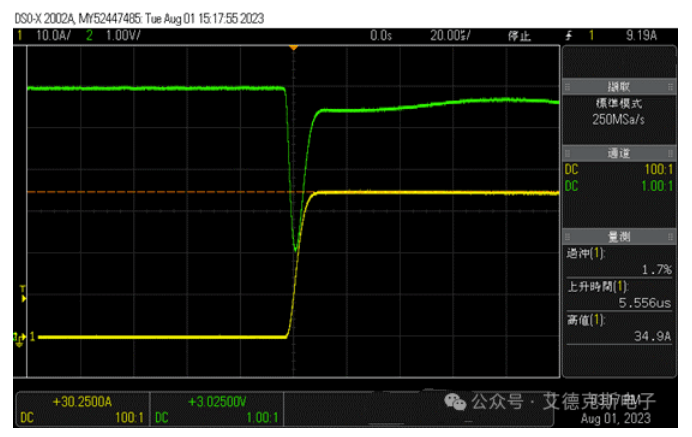

圖三IT8733P+CC電流實測12A/μs

動態測試:0.01s,50%,A=1A,B=120A

除了電子負載本身需具有高速的硬件指標,測試線接線方案也影響著測試的實際效果。根據法拉第電磁感應定律,一個變化的磁場會在導線上產生一個感應電動勢(電壓)。當電流嘗試在很短的時間內發生較大的變化時,導線的電感會產生一個與電流變化方向相反的感應電動勢,從而阻礙這種電流變化。因此當電流變化較大時,由于導線的電感性,會在導線上產生較大的壓降。這就是為什么在高速數字電路、射頻電路和電力傳輸中,電感效應是非常重要的考慮因素。在這些應用中,導線、電路板走線甚至元件的布局都可能成為關鍵因素,因為它們都可能引入不希望的電感效應。

導線的電感效應

我們用具體測試帶大家認識一下導線的電感效應。如圖四所示,測試電源采用ITECH大功率直流電源IT6532D(6V/60A),后端采用長導線連接ITECH多通道直流電子負載IT8732P+(機框:IT8702P),可以看到長導線電感大導致的直流電阻大,負載端電壓瞬間下降5.5V至0.5V左右,此時由于電壓過低,負載呈現飽和狀態,雖然負載具有優秀的動態速度但因導線原因會有電流過沖。

圖四6A/μs恒流35A長導線

通道1:電流,通道2:負載端口電壓

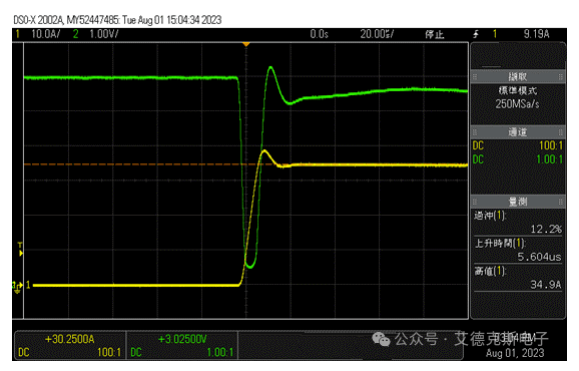

當使用優化的導線接線替代長導線,在同樣的測試條件下,我們可以看到如圖二所示,電壓下降4V至2V左右,此時負載IT8732P+可以迅速帶載并無電流過沖。所以在客戶需要較大電流變化率的場合,建議更換低電感導線,這樣才能得到完美低干擾的測試數據,也能保護待測物不受過沖電流的沖擊。

圖五、短導線實測效果

如何減小導線的電感效應?

降低外接正負導線的電感性是電子設計中的常見考慮。以下是一些建議和方法,用于減小導線的電感效應:

1、縮短導線長度:電感與導線的長度成正比。縮短導線的長度可以直接降低其電感。

2、使用更寬的導線:導線的電感與其尺寸和形狀有關。較寬的導線具有較低的電感。

3、使用并聯導線:多根并行的導線可以分擔電流,并且總的電感會下降。

4、優化布線:將正負導線并行放置并靠得很近,可以使得它們的磁場相互抵消,從而降低總的電感。

5、使用屏蔽或同軸電纜:這些電纜的設計可以將中心導體和外層屏蔽間的電感降至低。

6、使用低電感設計的連接器和端子:市場上有些連接器和端子被設計為具有低電感特性,適用于高頻或高速應用。

7、添加去耦電容:在電源和負載之間添加去耦電容可以提供一個低阻抗的路徑,對于高頻信號或電流尖峰來說,這可以降低電感的影響。

對于特定的應用或特定的條件,可能需要采用一種或多種策略組合以達到佳效果。

掃一掃關注我們