準確的能量損失測量是雙脈沖測試的關鍵目標之一。消除電壓和電流探頭之間的時序偏差是在示波器上進行精確功率和能量測量的關鍵步驟。

雙脈沖測試軟件(WBG-DPT)可在4系列,5系列和6系列mso上使用,包括專門為雙脈沖測試設計的新桌面技術。這種新穎的方法與傳統的方法有很大的不同,而且速度快得多。它可以節省幾個小時的測試時間。

該技術適用于使用fet或igbt的功率轉換器。為了這篇文章的目的,我們將使用FET術語來保持簡單。

為什么抗扭斜?

在任何功率變換器的設計中,開關過程中的能量損失必須小化。這種能量損失可以用示波器測量。一般的方法是將并發電壓和電流樣本相乘以產生功率波形。

P(t)=v(t)*i(t)

由于功率波形表示隨時間的能量消耗,因此可以通過對功率波形進行積分來確定能量:

E=∫p(t)dt

為了使這些能量損耗測量準確,電流和電壓波形的轉換應及時對齊。因此,為了實現有意義的能量損失測量,設計人員必須糾正由測試夾具和探頭引入的不同延遲。

傳統上,在測試裝置上開始任何測量之前計算探針之間的傾斜。對于低壓應用,可以使用函數發生器和桌面適配器(Tektronix P/N 067-1686-03)進行校準。然而,這種方法并不是高電壓和大電流應用的佳選擇。

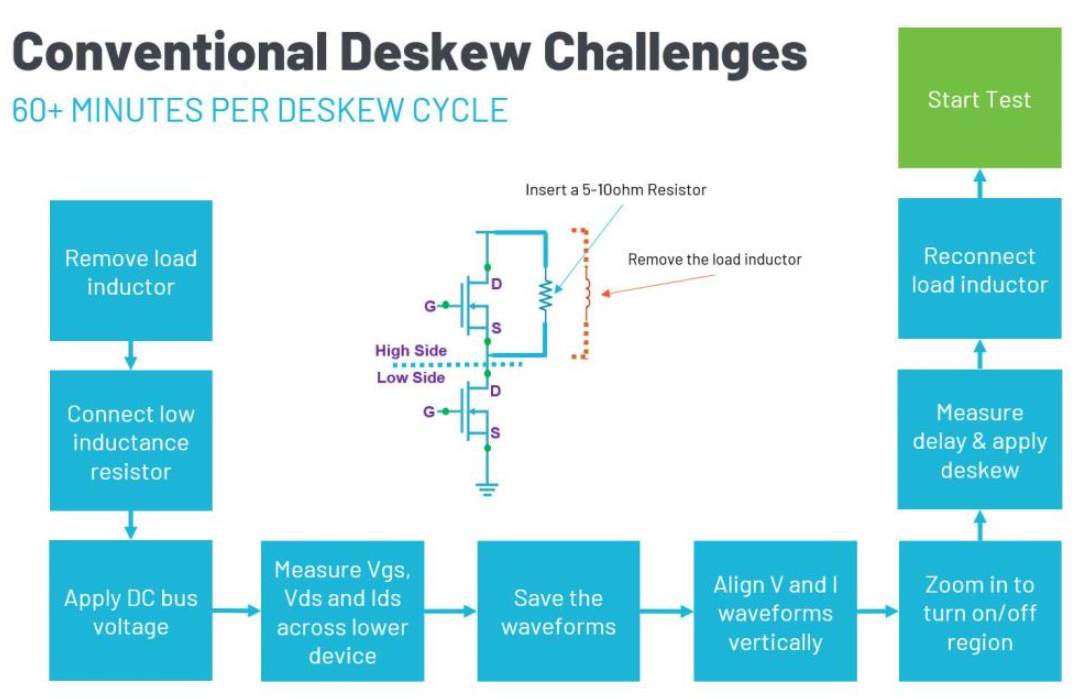

校準高功率、低側漏源電壓(VDS)和漏極電流(ID)測量的傳統技術需要重新布線測試裝置。負載電感必須拆下并用電阻器代替。然后進行測量,并將VDS和ID測量值對齊。這個過程可能需要一個小時或更長時間。

傳統的辦公桌需要修改電路

圖1所示。解決傾斜的傳統方法包括去除負載電感并用電阻器代替它。

一種新的辦公桌方法

泰克WBG-DPT解決方案的業界首創的基于軟件的工作臺技術消除了重新布線的需要,并在進行雙脈沖測量后執行。在新方法中,獲取漏極電流(ID)并將其用作參考波形。在導通過程中,使用測試電路的參數化模型計算低側VDS對準波形。校準波形參考ID波形,并且相對于ID將具有零傾斜。傾斜算法確定了計算的VDS對準波形與測量的VDS波形之間的傾斜。然后對VDS測量通道進行傾斜校正。

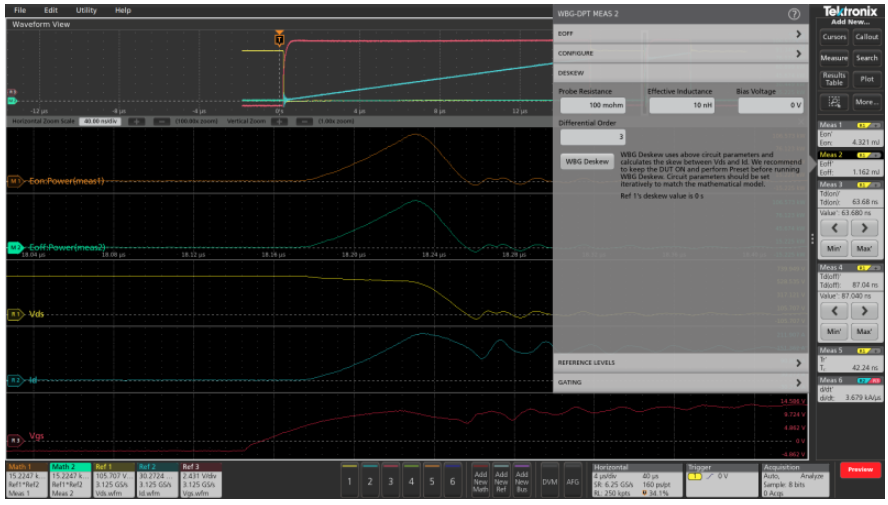

配置雙脈沖測試軟件工作臺

圖2。采用這種新方法,在測試后進行桌面顯示。參數在Deskew菜單中指定。

桌面程序

如上所述,可以在測量完成后進行測試。可以開始雙脈沖測試,而不必擔心VDS和ID之間的傾斜,然后選擇Deskew設置并提供以下參數:

探頭電阻-假定是一個電流觀察電阻(CVR)或分流電阻在這篇文章

有效的“環路”電感

偏置電壓(關斷時低側FET上的平均VDS)

微分階(模型用于平滑的濾波器階)

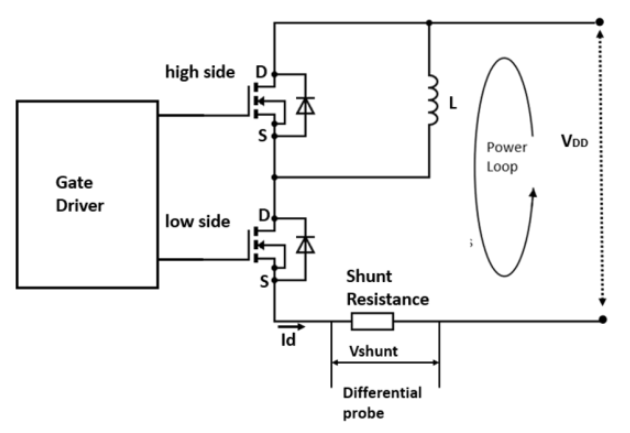

等效電路用于建立傾斜對準波形

圖3。用于構建VDS_low對準波形的等效電路。這個電路假設一個電流觀察電阻被用來測量ID。

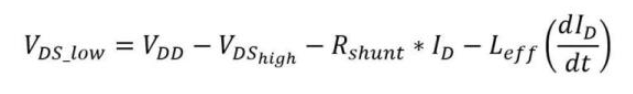

在桌面菜單中輸入的參數用于構建VDS校準波形。使用基爾霍夫電壓定律構建波形:

基爾霍夫電壓定律被用來幫助構建波形

地點:

VDD-VDS_high表示電源軌電壓和高側場效應管的壓降。注意,在導通期間,這將是恒定的,因為VDD是固定的,而VDS_high是通過高側場效應管主體二極管的電壓。

分流是指電流分流的電阻。

ID是測量的漏極電流,基于Rshunt上的下降。

dID/dt是漏極電流的測量變化率。

左為整個功率回路的有效電感。

在導通期間,VDD-VDS_high實際上是恒定的,如上所述。Rshunt和Leff也是常數。這意味著建模的VDS_low對準波形是ID的函數。

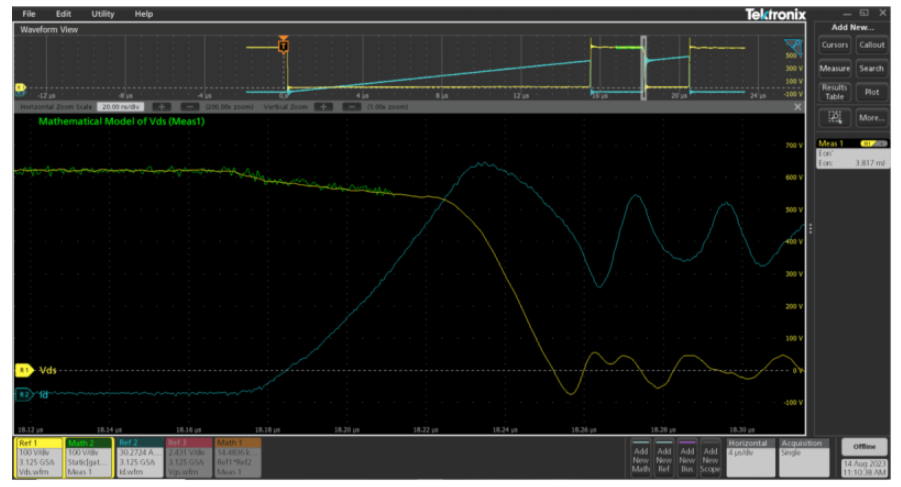

參數配置完成后,用戶按下WBG桌面按鈕。系統根據給定的參數和漏極電流生成VDS的數學模型。此對齊波形顯示在屏幕上。

圖4。由ID計算得到的VDS對準波形與實測VDS波形進行了比較。偏差是校準波形和測量波形之間的時間差。一旦計算,斜度可以從ID波形中去除。

有效電感,Leff,是一個“集總”元素,考慮如上所示的整個回路。因此,Leff通常是未知的,并且將其撥通將是一個迭代過程。傾斜過程可以很容易地重復運行,并可以對Leff進行調整,直到計算的對準波形和測量的VDS波形具有相同的形狀。如果模擬的VDS對準波形與實測的VDS波形形狀存在差異,可以調整參數,重新運行工作臺。

一旦參數準確地代表了系統,建模的對準波形將具有相同的形狀,系統可以確定和糾正偏差。傾斜值顯示在傾斜設置中,并自動應用于VDS信號連接的通道。

這種新工藝精確地計算了傾斜,并將傾斜時間從一個小時或更長時間減少到5到10分鐘。

掃一掃關注我們